## **DSP HDL Toolbox**™ Reference

# MATLAB&SIMULINK®

R

**R**2022**b**

#### **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\searrow$

508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

DSP HDL Toolbox<sup>™</sup> Reference

© COPYRIGHT 2022 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

March 2022Online onlyNew for Version 1.0 (Release 2022a)September 2022Online onlyRevised for Version 1.1 (Release 2022b)

## Contents

|   | Blocks         |

|---|----------------|

| 1 |                |

|   |                |

|   |                |

|   | System Objects |

| 2 |                |

## **Blocks**

## **CIC Interpolator**

Interpolate signal using CIC filter

Library: DSP HDL Toolbox / Filtering

#### Description

The CIC Interpolator block interpolates an input signal by using a cascaded integrator-comb (CIC) interpolation filter. CIC interpolation filters are a class of linear phase finite impulse response (FIR) filters consisting of a comb part and an integrator part. The CIC interpolation filter structure consists of *N* sections of cascaded comb filters, a rate change factor of *R*, and *N* sections of cascaded integrators. For more information about CIC interpolation filters, see "Algorithms" on page 1-7.

The block supports these combinations of input and output data.

- Scalar input and scalar output Support for fixed and variable interpolation rates

- Scalar input and vector output Support for fixed interpolation rates only

- Vector input and vector output Support for fixed interpolation rates only

The block provides an architecture suitable for HDL code generation and hardware deployment.

#### Ports

#### Input

#### data — Input data

scalar | column vector

Input data, specified as a scalar or a column vector with a length from 1 to 64.

The input data must be a signed integer or signed fixed point with a word length less than or equal to 32.

Data Types: int8 | int16 | int32 | signed fixed point Complex Number Support: Yes

#### valid — Indicates valid input data

scalar

Control signal that indicates if the input data is valid. When **valid** is 1 (true), the block captures the values from the input **data** port. When **valid** is 0 (false), the block ignores the values from the input **data** port.

Data Types: Boolean

#### **R** — Variable interpolation rate

scalar

Use this port to dynamically specify the variable interpolation rate during run time.

This value must have the data type fixdt(0, 12, 0) and must be an integer in the range from 1 to the **Interpolation factor (Rmax)** parameter value.

#### Dependencies

To enable this port, on the **Main** tab, set the **Interpolation factor source** parameter to **Input** port.

Data Types: fixdt(0,12,0)

#### reset — Clears internal states

scalar

Control signal that clears internal states. When **reset** is 1 (true), the block stops the current calculation and clears internal states. When the **reset** is 0 (false) and the input **valid** is 1 (true), the block captures data for processing.

For more reset considerations, see the "Reset Signal" section on the "Hardware Control Signals" page.

#### Dependencies

#### To enable this port, on the **Control Ports** tab, select the **Enable reset input port** parameter.

Data Types: Boolean

#### Output

#### data — CIC-interpolated output data

scalar | column vector

CIC-interpolated output data, returned as a scalar or a column vector with a length from 1 to 64. You can define the data type of this output by setting the **Output data type** parameter on the **Data Types** tab.

Data Types: int8 | int16 | int32 | signed fixed point Complex Number Support: Yes

#### valid — Indicates valid output data

scalar

Control signal that indicates if the data from the output **data** port is valid. When **valid** is 1 (true), the block returns valid data from the output **data** port. When **valid** is 0 (false), the values from the output **data** port are not valid.

Data Types: Boolean

#### ready — Indicates block is ready for new input data

scalar

Control signal that indicates that the block is ready for new input data sample on the next cycle. When **ready** is 1 (true), you can specify the **data** and **valid** inputs for the next time step. When **ready** is 0 (false), the block ignores any input data in the next time step.

Data Types: Boolean

#### **Parameters**

#### Main

#### Interpolation factor source — Source of interpolation factor

Property (default) | Input port

Select whether the block operates with a fixed or variable interpolation rate.

- Property Use a fixed interpolation rate specified from the Interpolation factor (R) parameter.

- Input port Use a variable interpolation rate specified from the  ${\bf R}$  input port.

**Note** The block does not support variable interpolation for these two combinations of input and output:

- Scalar input and vector output

- Vector input and vector output

#### Interpolation factor (R) — Interpolation factor

2 (default) | integer from 1 to 2048

Specify the interpolation factor rate at which the block interpolates the input. This value must be an integer. The range of available values depends on the type of input and output data.

| Input Data | Output Data | Interpolation factor (R) Valid Values |

|------------|-------------|---------------------------------------|

| Scalar     | Scalar      | Integer from 1 to 2048                |

| Scalar     | Vector      | Integer from 1 to 64                  |

| Vector     | Vector      | Integer from 1 to 64                  |

**Note** For vector inputs, select the interpolation factor rate and input vector length such that their multiplication value does not exceed 64.

#### Dependencies

To enable this parameter, set the Interpolation factor source parameter to Property.

#### Interpolation factor (Rmax) — Upper bound of variable interpolation factor

2 (default) | integer from 1 to 2048

Specify the upper bound of the range of valid values for the  ${f R}$  input port.

**Note** The block does not support variable interpolation for these two combinations of input and output:

- Scalar input and vector output

- Vector input and vector output

#### Dependencies

To enable this parameter, set the **Interpolation factor source** parameter to **Input** port.

#### Differential delay (M) — Differential delay

1 (default) | 2

Specify the differential delay of the comb part of the block.

#### Number of sections (N) — Number of integrator and comb sections

2 (default) | 1 | 3 | 4 | 5 | 6

Specify the number of sections in either the comb part or the integrator part of the block.

## Minimum number of cycles between valid input samples — Minimum number of cycles between valid input samples

1 (default) | factors or multiples of *R*

Specify the minimum number of cycles between the valid input samples as 1, factors of R, or multiples of R based on the type of input and output data, where R is the interpolation factor.

| Input Data |        | Minimum Number of Cycles Between<br>Valid Input Samples |

|------------|--------|---------------------------------------------------------|

| Scalar     | Scalar | greater than or equal to R                              |

| Scalar     | Vector | factors less than R                                     |

| Vector     | Vector | 1                                                       |

#### Dependencies

To enable this parameter, set the **Interpolation factor source** parameter to **Property**.

#### Gain correction — Output gain compensation

off (default) | on

Select this parameter to compensate for the output gain of the block.

The latency of the block changes depending on the type of input, the interpolation you specify, the number of sections, and the value of this parameter. For more information on the latency of the block, see "Latency" on page 1-10.

#### Data Types

#### Output data type — Data type of output

Full precision (default) | Same word length as input | Minimum section word lengths

Select the data type for the output data.

- Full precision The output data type has a word length equal to the input word length plus gain bits.

- Same word length as input The output data type has a word length equal to the input word length.

- Minimum section word lengths The output data type uses the word length you specify in the **Output word length** parameter.

#### Output word length - Word length of output

16 (default) | integer from 2 to 104

Specify the word length of the output as an integer from 2 to 104.

#### Dependencies

To enable this parameter, set the **Output data type** parameter to Minimum section word lengths.

#### **Control Ports**

#### Enable reset input port — Option to enable reset input port

#### off (default) | on

Select this parameter to enable the **reset** input port. The reset signal implements a local synchronous reset of the data path registers.

For more reset considerations, see "Tips" on page 1-6.

## Use HDL global reset — Option to connect data path registers to generated HDL global reset signal

#### off (default) | on

Select this parameter to connect the generated HDL global reset signal to the data path registers. This parameter does not change the appearance of the block or modify simulation behavior in Simulink<sup>®</sup>. When you clear this parameter, the generated HDL global reset clears only the control path registers. The generated HDL global reset can be synchronous or asynchronous depending on the **HDL Code Generation > Global Settings > Reset type** parameter in the model Configuration Parameters.

For more reset considerations, see "Tips" on page 1-6.

#### Tips

#### **Reset Behavior**

• By default, the CIC Interpolator block connects the generated HDL global reset to only the control path registers. The two reset parameters, **Enable reset input port** and **Use HDL global reset**, connect a reset signal to the data path registers. Because of the additional routing and loading on the reset signal, resetting data path registers can reduce synthesis performance.

- The **Enable reset input port** parameter enables the **reset** port on the block. The reset signal implements a local synchronous reset of the data path registers. For optimal use of FPGA resources, this option does not connect the reset signal to registers targeted to the DSP blocks of the FPGA.

- The **Use HDL global reset** parameter connects the generated HDL global reset signal to the data path registers. This parameter does not change the appearance of the block or modify simulation behavior in Simulink. The generated HDL global reset can be synchronous or asynchronous depending on the **HDL Code Generation** > **Global Settings** > **Reset type** parameter in the model Configuration Parameters. Depending on your device, using the global reset might move registers out of the DSP blocks and increase resource use.

- When you select the **Enable reset input port** and **Use HDL global reset** parameters together, the global and local reset signals clear the control and data path registers.

#### **Reset Considerations for Generated Test Benches**

- FPGA-in-the-loop (FIL) initialization provides a global reset but does not automatically provide a local reset. With the default reset parameters, the data path registers that are not reset can result in FIL mismatches if you run the FIL model more than once without resetting the board. Select **Use HDL global reset** to reset the data path registers automatically, or select **Enable reset input port** and assert the local reset in your model so the reset signal becomes part of the Simulink FIL test bench.

- The generated HDL test bench provides a global reset but does not automatically provide a local reset. With the default reset parameters and the default register reset Configuration Parameters, the generated HDL code includes an initial simulation value for the data path registers. However, if you are concerned about X-propagation in your design, you can set the HDL Code Generation > Global Settings > Coding style > No-reset register initialization parameter in Configuration Parameters to Do not initialize. In this case, with the default block reset parameters, the data path registers that are not reset can cause X-propagation on the data path at the start of HDL simulation. Select Use HDL global reset to reset the data path registers automatically, or select Enable reset input port and assert the local reset in your model so the reset signal becomes part of the generated HDL test bench.

#### Algorithms

#### **CIC Interpolation Filter**

The transfer function of a CIC interpolation filter is

$$H(z) = \left[\sum_{k=0}^{RM-1} z^{-k}\right]^{N} = \frac{(1-z^{-RM})^{N}}{(1-z^{-1})^{N}} = \frac{(1-z^{-RM})^{N}}{1} \cdot \frac{1}{(1-z^{-1})^{N}} = H_{\rm C}N(z) \cdot H_{\rm I}N(z)$$

- $H_{\rm C}$  is the transfer function of the comb part of the CIC filter.

- $H_{\rm I}$  is the transfer function of the integrator part of the CIC filter.

- N is the number of sections in either the comb part or integrator part of the filter. This value does not represent the total number of sections throughout the entire filter.

- *R* is the interpolation factor.

- *M* is the differential delay.

#### **CIC Filter Structure**

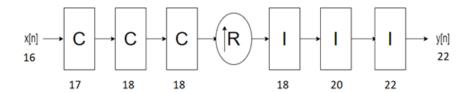

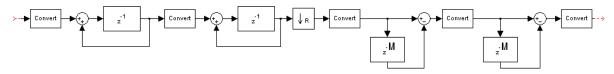

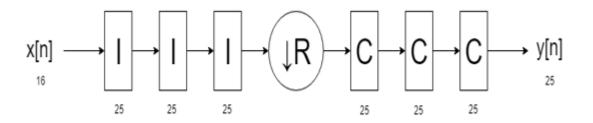

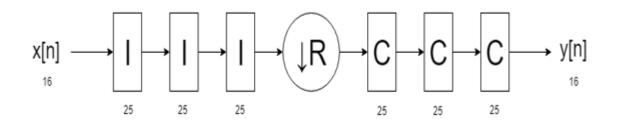

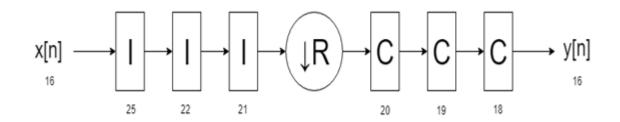

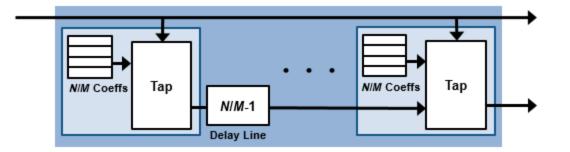

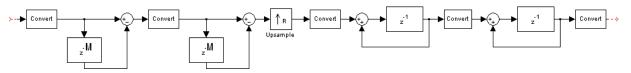

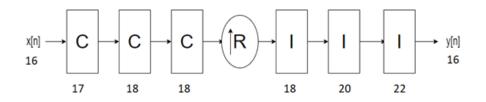

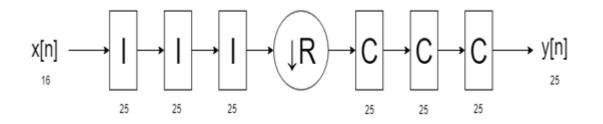

The CIC Interpolator block has the CIC filter structure shown in this figure. The structure consists of N sections of cascaded comb filters, a rate change factor of R, and N sections of cascaded integrators [1].

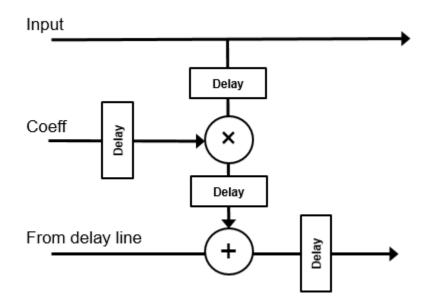

You can locate the unit delay in the integrator part of the CIC filter in either the feedforward or feedback path. These two configurations yield an identical filter frequency response. However, the numerical outputs from these two configurations are different due to the latency of the block. Because this configuration is preferred for HDL implementation, this block puts the unit delay in the feedforward path of the integrator.

#### **Fixed and Variable Interpolation**

The block upsamples the comb stage output using R, either using the fixed interpolation rate provided using the **Interpolation factor (R)** parameter or the variable interpolation rate provided using the **R** input port. At the upsampling stage, the block uses a counter to count the valid input samples, which depend on the interpolation rate. Whenever the interpolation rate changes, the block resets and starts a new calculation from the next sample. This mechanism prevents the block from accumulating false values. Then, the block provides the interpolated output to the integrator part of the CIC filter.

#### **Gain Correction**

The gain of the CIC interpolation filter at each stage is given by

$$G_{i} = \left\{ \frac{2^{i} \qquad i = 1, 2, ..., N}{\frac{2^{2N-i}(RM)^{i-N}}{R}} = N + 1, ..., 2N \right\}.$$

- $G_i$  is the gain at *i*th stage.

- *R* is the **Interpolation factor (R)** parameter value.

- *M* is the **Differential delay (M)** parameter value.

- *N* is the **Number of sections (N)** parameter value.

The output of the block is amplified by a specific gain value. This gain equals the gain of the 2Nth stage of the CIC interpolation filter and is given by  $Gain = \frac{(R \ge M)^N}{R}$ .

The block implements gain correction in two parts: coarse gain and fine gain. In coarse gain correction, the block calculates the shift value, adds the shift value to the fractional bits to create a numeric type, and performs a bit-shift left and reinterpretcast. In fine gain correction, the block divides the remaining gain with the coarse gain if the gain is not a power of 2. Then, the block multiplies the corrected coarse gain value by the inverse value of the fine gain. Before the block starts processing, all possible shift and fine gain values are precalculated and stored in an array.

You can modify this equation to  $Gain = 2^{cGain} \ge fGain$ . In this equation, *cGain* is the coarse gain and *fGain* is the fine gain. These gains are given by these equations.

- cGain = floor(log<sub>2</sub>Gain)

- $fGain = Gain/2^{cGain} = Gain \ge 2^{-cGain}$

To perform gain correction when the **Interpolation factor source** parameter is set to Input port, the block sets the output data type configured with the maximum interpolation rate and bit-shifts left for all of the values under the maximum interpolation rate. The bit-shift value is equal to  $Maximum \ gain \ - \log_2(current \ gain)$ .

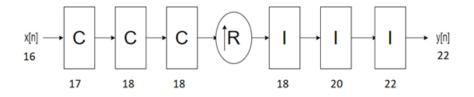

#### **Output Data Type**

The block outputs data based on the output data type selection. Consider a block with R, M, and N values of 8, 1, and 3, respectively, and an input width of 16. The word length at the *i*th internal stage is calculated as  $B_i = B_{\text{In}} + [\log_2(G_i)]$ , where:

- $G_i$  is the gain at *i*th stage.

- *B*<sub>In</sub> is the input word length.

- *B<sub>i</sub>* is the word length at *i*th stage.

The output word length is calculated as  $B_{Out} = B_{In} + N - 1$ , where  $B_{Out}$  is the output word length.

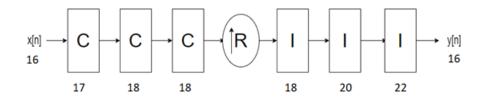

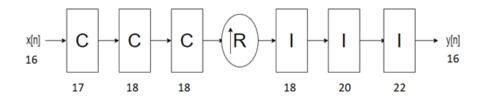

When you set the **Output data type** parameter to Full precision, the block outputs data with a word length of 22 by adding 6 gain bits to the input word length of 16. The word lengths of the internal comb and integrator stages are set to accommodate the bit growth.

When you set the **Output data type** parameter to Same word length as input, the block outputs data with a word length of 16, which is the same length as the input word length. The word lengths of the internal comb and integrator stages are set in the same way as in Full precision mode.

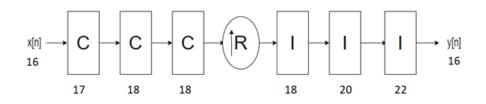

When you set the **Output data type** parameter to Minimum section word lengths and the **Output word length** parameter to 16, the block outputs data with a word length of 16. The word

lengths of the internal comb and integrator stages are set in the same way as in Full  ${\tt precision}$  mode.

#### Latency

The latency of the block changes depending on the type of input, the interpolation you specify, the number of sections, the value of the **Gain correction** parameter, and the value of the **Minimum number of cycles between valid input samples** parameter. This table shows the latency of the block. *N* is the number of sections, *vecLen* is the length of the vector, and *R* is the interpolation factor.

Common latency is equal to  $2 + (N \times (vecLen \times R)) + 3 \times N$ , when R is equal to 1 and is equal to  $3 + (N \times (vecLen \times R)) + 3 \times N$ , when R is greater than 1.

| Input<br>Data | Output<br>Data | Interpolat<br>ion Type |     | Minimum<br>number<br>of cycles<br>between<br>valid<br>input<br>samples<br>(NumCyc<br>les) | Latency in Clock Cycles                                                                                                                                                                                                                                                 |

|---------------|----------------|------------------------|-----|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Scalar        | Scalar         | Fixed                  | off | NumCycle<br>s = R and<br>> R                                                              | 3 + <i>N</i> .<br>2 + <i>N</i> , when <i>R</i> = 1.                                                                                                                                                                                                                     |

|               |                |                        | on  | s = R and                                                                                 | 3 + N + 9.<br>2 + N + 9, when $R = 1.$                                                                                                                                                                                                                                  |

| Scalar        | Scalar         | Variable               | off | NA                                                                                        | $3 + N + 2 \ge R_{max}$ .<br>2 + N, when $R_{max} = 1$ .                                                                                                                                                                                                                |

|               |                |                        | on  | NA                                                                                        | $2 + N + 2 \ge R_{max} + 9.$<br>2 + N + 9, when $R_{max} = 1.$                                                                                                                                                                                                          |

| Scalar        | Vector         | Fixed                  | off | NumCycle<br>s = 1                                                                         | Common latency + 1, when R is greater than N.<br>Common latency, when R is less than or equal to N.<br>Common latency - $(1 + floor(N/(3 \times R)))$ , when R is<br>less than N and (vecLen == 2 && (R == 2 && (N == 4))    N == 5    N == 6))    (R == 3 && N == 6)). |

| Input<br>Data | Output<br>Data | Interpolat<br>ion Type | Gain<br>Correctio<br>n |                   | Latency in Clock Cycles                                                                                                                                                                                                                                                                                                                    |

|---------------|----------------|------------------------|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                |                        |                        | NumCycle<br>s < R | $3 + N + ((R + 1) \times N + 2) + 1 + (N - 1) \times NumCycles.$                                                                                                                                                                                                                                                                           |

|               |                |                        | on                     | NumCycle<br>s = 1 | Common latency + 1 + 9, when R is greater than N.<br>Common latency + 9, when R is less than or equal to<br>N.<br>Common latency - $(1 + floor(N/(3 \times R))) + 9$ , when R<br>is less than N and (vecLen == 2 && (R == 2 && (N == 4))<br>$= 4 \parallel N == 5 \parallel N == 6$ ) $\parallel (R == 3 & N == 6)$ .                      |

|               |                |                        |                        | NumCycle<br>s < R | $3 + N + ((R + 1) \times N + 2) + 1 + (N - 1) \times NumCycles + 9$ .                                                                                                                                                                                                                                                                      |

| Vector        | Vector         | Fixed                  | off                    | NumCycle<br>s = 1 | Common latency<br>Common latency - 1, when (vecLen == 2 && (R ==<br>2 && (N == 4    N == 5    N == 6))    (R== 3 && N<br>== 6))    (vecLen == 3 && (R == 2 && N == 6)).<br>Common latency - ((N >1) + (N > 4)), when R = 1<br>and vecLen == 2.<br>Common latency - ((N > (vecLen - 1)), when R = 1<br>and vecLen > 2.                      |

|               |                |                        | on                     | NumCycle<br>s = 1 | Common latency + 9.<br>Common latency - 1 + 9, when (vecLen == 2 && (R<br>== 2 && (N == 4    N == 5    N == 6))    (R== 3<br>&& N == 6))    (vecLen == 3 && (R == 2 && N ==<br>6)).<br>Common latency - ((N > 1) + (N > 4)) + 9, when R =<br>1 and vecLen == 2.<br>Common latency - ((N > (vecLen - 1)) + 9, when R<br>= 1 and vecLen > 2. |

**Note** The block does not support variable interpolation for these two combinations of input and output:

• Scalar input and vector output

• Vector input and vector output

#### Scalar Input

This section shows the output of the block for a scalar input with different *R*, *M*, and *N* values.

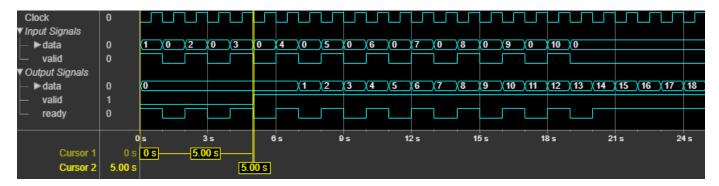

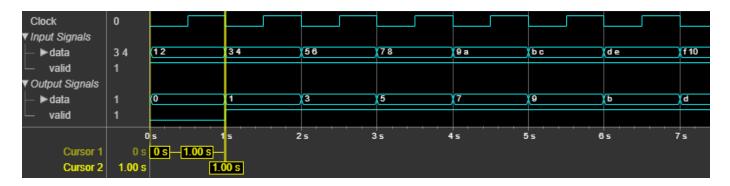

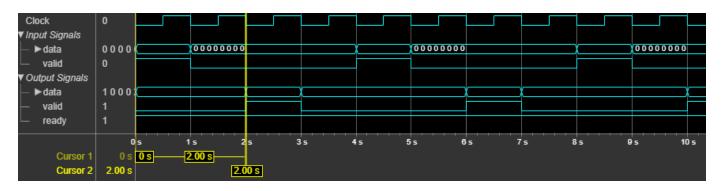

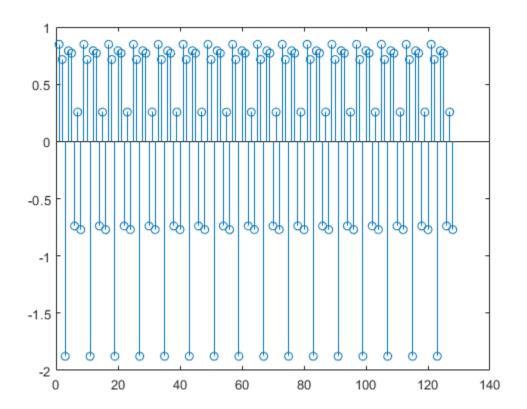

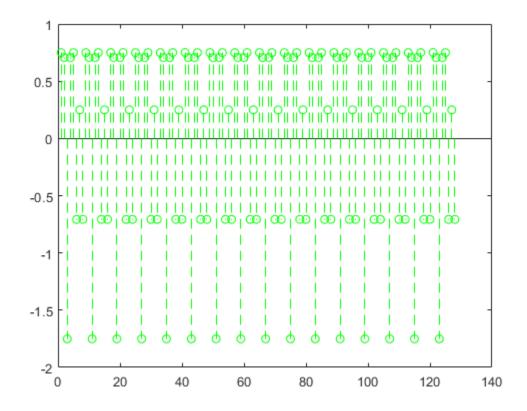

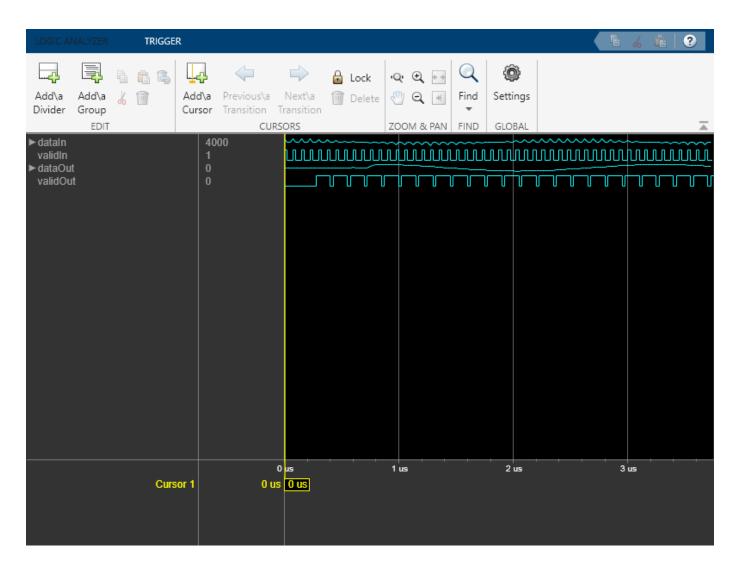

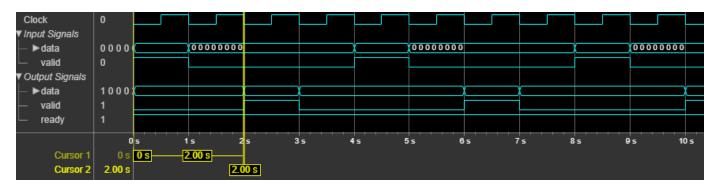

This figure shows the output of the block with the default configuration (that is, with a fixed interpolation rate and R, M, and N values of 2, 1, and 2, respectively). The latency of the block is 5 clock cycles and is calculated as 3 + N, where N is the number of sections.

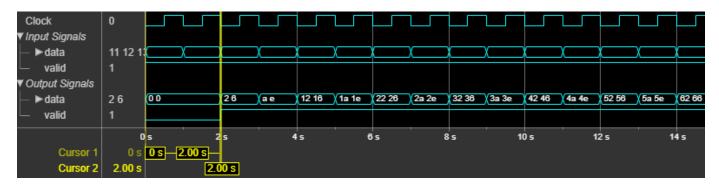

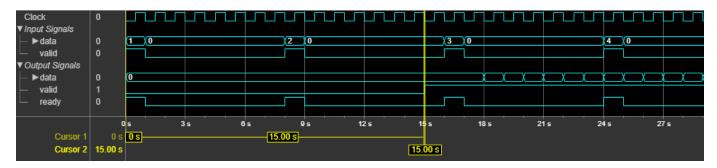

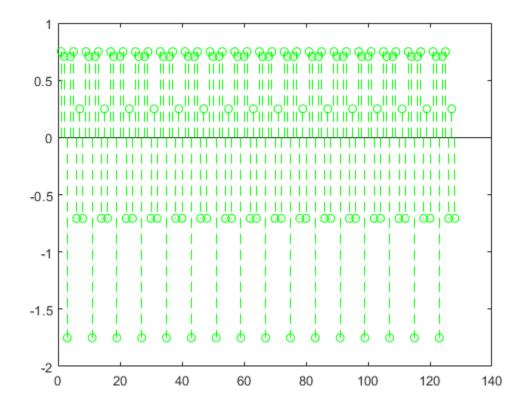

This figure shows the output of the block with a fixed interpolation rate, R, M, and N values of 8, 1, and 3, respectively, and the **Gain correction** parameter selected. The latency of the block is 15 clock cycles and is calculated as 3 + N + 9, where N is the number of sections.

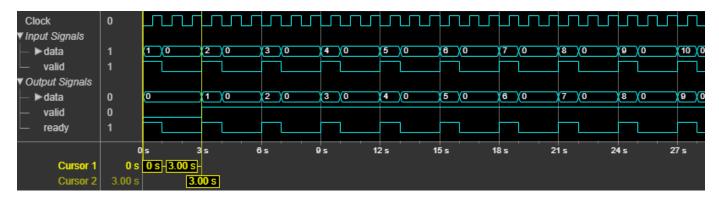

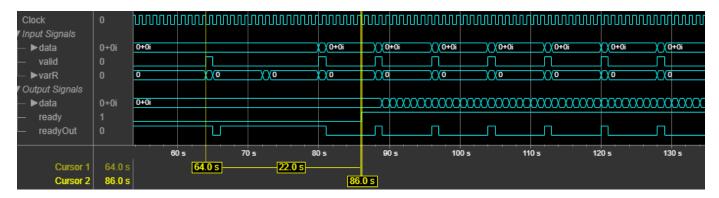

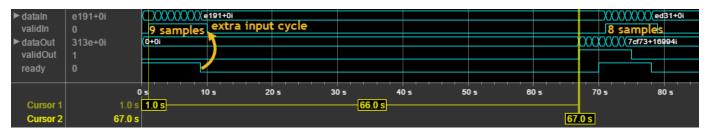

This figure shows the output of the block with variable interpolation rate (**R** input port) values of 2, 4, and 8 and with *M* and *N* values of 1 and 3, respectively. In this case, the **Gain correction** parameter is cleared. The block accepts **R** port value changes only when the **valid** input port is 1. The latency of the block is 22 clock cycles and is calculated as  $3 + N + 2 \ge R_{max}$ , where *N* is the number of sections and  $R_{max}$  is the maximum interpolation factor.

| Clock<br>I Input Signals     | 0      | www  | www    | www  | mmm        | MMM      | www.m         | www      | mm        | MMM     | www.ww                                  |

|------------------------------|--------|------|--------|------|------------|----------|---------------|----------|-----------|---------|-----------------------------------------|

| — ►data                      | 0+0i   | 0+0i |        |      | ( ) ( 0+0i | <u> </u> | X X 0+0i      | () (0+0i | ) ( (0+0i | X (0+0i | χ χ0+0i                                 |

| — valid                      |        |      |        |      |            |          |               |          |           |         |                                         |

| — ▶varR                      |        | 0    | 0      | χχο  | X XO       | XXo      |               | ))(0     |           |         | XXO                                     |

| V Output Signals             |        |      |        |      |            |          |               |          |           |         |                                         |

| — ►data                      | 0+0i   | 0+0i |        |      |            |          | 0000000000000 | 00000000 | 00000000  |         | 000000000000000000000000000000000000000 |

| — ready                      |        |      |        |      |            |          |               |          |           |         |                                         |

| <ul> <li>readyOut</li> </ul> |        |      |        |      |            |          |               |          |           |         |                                         |

|                              |        | 60   | 5      | 70 s | 80 s       | 90 s     | 100 s         | 11       | 10 s      | 120 s   | 130 s                                   |

| Cursor 1                     | 64.0 s |      | 64.0 s | 22   | ) s        | -        |               |          |           |         |                                         |

| Cursor 2                     | 86.0 s | ;    |        |      | 86         | 5.0 s    |               |          |           |         |                                         |

#### **Vector Input**

This section shows the output of the block for a vector input with different *R*, *M*, and *N* values.

This figure shows the output of the block for a two-element column vector input with the default configuration (that is, with a fixed interpolation rate and R, M, and N values of 2, 1, and 2, respectively). The latency of the block is 17 clock cycles.

| Clock              | 0          | MMMMM      | www   | w    | www.ww    | www.ww  | www.ww | hunnun | wwww | www.ww | wwwww | nnn  |

|--------------------|------------|------------|-------|------|-----------|---------|--------|--------|------|--------|-------|------|

| ▼ Input Signals    | 10.00      |            |       |      |           |         |        |        |      |        |       |      |

| — ►data<br>— valid | 19 20<br>1 | 0000000000 | 19 20 |      |           |         |        |        |      |        |       |      |

| ▼ Output Signals   |            |            |       |      |           |         |        |        |      |        |       |      |

| →data              | 0012       | 0000       |       | 000  | 000000394 | 0 39 38 |        |        |      |        |       |      |

| └─ valid           | 1          |            |       |      |           |         |        |        |      |        |       |      |

|                    |            | 0 s        | 10 s  | 20   | )s 31     | 0s 4    | 10s 5  | 50s 6  | 0s 7 | 0s 8   | 0s 9  | ló s |

| Cursor 1           |            |            | .00 s |      |           |         |        |        |      |        |       |      |

| Cursor 2           | 17.00 క    | 5          | 17.   | )0 s |           |         |        |        |      |        |       |      |

This figure shows the output of the block for an eight-element column vector input with a fixed interpolation rate, *R*, *M*, and *N* values of 8, 1, and 3, respectively, and the **Gain correction** parameter selected. The latency of the block is 213 clock cycles.

| Clock<br>▼ Input Signals | 0        |                  |                | งนักบานการเกมา | น่นแบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบ |            |           |           | ſ////  |       | บบบบบบานบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบบ |      |            |

|--------------------------|----------|------------------|----------------|----------------|-----------------------------------------|------------|-----------|-----------|--------|-------|-----------------------------------------|------|------------|

| ⊢ ► data<br>valid        | 73 74 75 | ((((()()()(73 74 | 75 76 77 78 79 | 30             |                                         |            |           |           |        |       |                                         |      |            |

| ▼ Output Signals         |          |                  |                |                |                                         |            |           |           |        |       |                                         |      |            |

| — ►data<br>— valid       | 0000.0   | 0000000          | 000000000      | 000000000      | 000000000                               | 0000000000 | 000000000 | 000000000 | 00000  |       |                                         |      | 00000      |

|                          | 0        | s                | 20 s           | 40s 6          | 60s 8                                   | 0s 10      | 0s 12     | 0s 14     | 10s 16 | 0s 18 | 0s 20                                   | 0 s  | 220        |

| Cursor 1                 |          | 0 s              |                |                |                                         |            | 213.0 s   |           |        |       |                                         |      |            |

| Cursor 2                 | 213.0 s  |                  |                |                |                                         |            |           |           |        |       |                                         | 213. | <u>0 s</u> |

#### Performance

The performance of the synthesized HDL code varies with your target and synthesis options. It also varies based on the input data type.

This table shows the resource and performance data synthesis results of the block for a scalar input with fixed and variable interpolation rates and for a two-element column vector of type fixdt(1,16,0) with a fixed interpolation rate when R, M, and N are 2, 1, and 2, respectively. The generated HDL code is targeted to the Xilinx<sup>®</sup> Zynq<sup>®</sup>- 7000 ZC706 Evaluation Board.

| Input Data | Interpolation Type | Slice LUTs |     | Maximum Frequency in<br>MHz |

|------------|--------------------|------------|-----|-----------------------------|

| Scalar     | Fixed rate         | 68         | 90  | 844.12                      |

|            | Variable rate      | 143        | 115 | 451.83                      |

| Vector     | Fixed rate         | 480        | 921 | 376.51                      |

The resources and frequencies vary based on the type of input data, R, M, and N values, and other parameter values selected in the block mask. Using a vector input can increase the throughput, however, doing so also increases the number of hardware resources that the block uses.

#### **Version History**

Introduced in R2022a

#### References

[1] Hogenauer, E. "An Economical Class of Digital Filters for Decimation and Interpolation." IEEE Transactions on Acoustics, Speech, and Signal Processing 29, no. 2 (April 1981): 155–62. https://doi.org/10.1109/TASSP.1981.1163535.

#### **Extended Capabilities**

#### C/C++ Code Generation

Generate C and C++ code using Simulink® Coder<sup>™</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

#### HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder<sup>m</sup> provides additional configuration options that affect HDL implementation and synthesized logic.

#### **HDL Architecture**

This block has one default HDL architecture.

#### **HDL Block Properties**

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays within your design. Distributed pipelining does not redistribute these registers. The default is $0$ . For more details, see "ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is $0$ . For more details, see "InputPipeline" (HDL Coder).                 |

| OutputPipeline | Number of output pipeline stages to insert in the generated code.        |

|----------------|--------------------------------------------------------------------------|

|                | Distributed pipelining and constrained output pipelining can move these  |

|                | registers. The default is 0. For more details, see "OutputPipeline" (HDL |

|                | Coder).                                                                  |

#### See Also

**Objects** dsphdl.CICInterpolator|dsphdl.CICDecimator

#### Blocks CIC Decimator

## **CIC Decimator**

Decimate signal using CIC filter Library: DSP HDL Toolbox / Filtering

#### Description

The CIC Decimator block decimates an input signal by using a cascaded integrator-comb (CIC) decimation filter. CIC decimation filters are a class of linear phase finite impulse response (FIR) filters consisting of a comb part and an integrator part. The CIC decimation filter structure consists of N sections of cascaded integrators, a rate change factor of R, and N sections of cascaded comb filters. For more information about CIC decimation filters, see "Algorithms" on page 1-20.

The block supports these combinations of input and output data.

- Scalar input and scalar output Support for fixed and variable decimation rates

- Vector input and scalar output Support for fixed decimation rates only

- Vector input and vector output Support for fixed decimation rates only

The block provides an architecture suitable for HDL code generation and hardware deployment.

#### Ports

#### Input

#### data — Input data

scalar | column vector

Input data, specified as a scalar or a column vector with a length from 1 to 64. The input data must be a signed integer or a signed fixed point with a word length less than or equal to 32. The **Decimation factor (R)** parameter must be an integer multiple of the input frame size.

Data Types: int8 | int16 | int32 | signed fixed point Complex Number Support: Yes

#### valid — Indicates valid input data

```

scalar

```

Control signal that indicates if the input data is valid. When **valid** is 1 (true), the block captures the values from the input **data** port. When **valid** is 0 (false), the block ignores the values from the input **data** port.

Data Types: Boolean

#### **R** — Variable decimation rate

scalar

Use this port to dynamically specify the variable decimation rate during run time.

This value must have the data type fixdt(0, 12, 0) and it must be an integer in the range from 1 to the **Decimation factor (Rmax)** parameter value.

#### Dependencies

To enable this port, on the Main tab, set the Decimation factor source parameter to Input port.

Data Types: fixdt(0,12,0)

#### reset — Clears internal states

scalar

Control signal that clears internal states. When **reset** is 1 (true), the block stops the current calculation and clears internal states. When the **reset** is 0 (false) and the input **valid** is 1 (true), the block captures data for processing.

For more reset considerations, see the "Reset Signal" section on the "Hardware Control Signals" page.

#### Dependencies

To enable this port, on the **Control Ports** tab, select the **Enable reset input port** parameter.

Data Types: Boolean

#### Output

#### data — CIC-decimated output data

scalar | column vector

The block returns filtered output data as a scalar or a column vector with a length from 1 to 64. You can define the data type of this output by setting the **Output data type** parameter on the **Data Types** tab.

#### valid — Indicates valid output data

scalar

Control signal that indicates if the data from the output **data** port is valid. When **valid** is 1 (true), the block returns valid data from the output **data** port. When **valid** is 0 (false), the values from the output **data** port are not valid.

Data Types: Boolean

#### **Parameters**

Main

#### Decimation factor source — Source of decimation factor

Property (default) | Input port

Select whether the block operates with a fixed or variable decimation rate.

Data Types: int8 | int16 | int32 | signed fixed point Complex Number Support: Yes

- Property Use a fixed decimation rate specified from the Decimation factor (R) parameter.

- Input port Use a variable decimation rate specified from the **R** input port.

**Note** For vector inputs, the block does not support variable decimation.

#### Decimation factor (R) — Decimation factor

2 (default) | integer from 1 to 2048

Specify the decimation factor rate at which the block decimates the input.

#### Dependencies

To enable this parameter, set the **Decimation factor source** parameter to **Property**.

#### Decimation factor (Rmax) — Upper bound of variable decimation factor

2 (default) | integer from 1 to 2048

Specify the upper bound of the range of valid values for the **R** input port.

**Note** For vector inputs, the block does not support variable decimation.

#### Dependencies

To enable this parameter, set the **Decimation factor source** parameter to Input port.

#### Differential delay (M) — Differential delay

1 (default) | 2

Specify the differential delay of the comb part of the block.

#### Number of sections (N) — Number of integrator and comb sections

2 (default) | 1 | 3 | 4 | 5 | 6

Specify the number of sections in either the comb part or the integrator part of the block.

#### Gain correction — Output gain compensation

off (default) | on

Select this parameter to compensate for the output gain of the block.

The latency of the block changes depending on the type of input, the decimation you specify, the number of sections, and the value of this parameter. For more information on the latency of the block, see "Latency" on page 1-23.

#### Data Types

#### Output data type — Data type of output

Full precision (default) | Same word length as input | Minimum section word lengths

Select the data type for the output data.

- Full precision The output data type has a word length equal to the input word length plus gain bits.

- Same word length as input The output data type has a word length equal to the input word length.

- Minimum section word lengths The output data type uses the word length you specify in the **Output word length** parameter. When you select this option, the block applies the pruning algorithm. For more information about the pruning algorithm, see [1].

#### Output word length — Word length of output

16 (default) | integer from 2 to 104

Specify the word length of the output.

**Note** When this value is 2, 3, 4, 5, or 6, the block can overflow the output data.

#### Dependencies

To enable this parameter, set the **Output data type** parameter to Minimum section word lengths.

#### **Control Ports**

#### Enable reset input port — Reset signal

off (default) | on

Select this parameter to enable the **reset** input port. The reset signal implements a local synchronous reset of the data path registers.

For more reset considerations, see "Tips" on page 1-20.

## Use HDL global reset — Option to connect data path registers to generated HDL global reset signal

#### off (default) | on

Select this parameter to connect the generated HDL global reset signal to the data path registers. This parameter does not change the appearance of the block or modify simulation behavior in Simulink. When you clear this parameter, the generated HDL global reset clears only the control path registers. The generated HDL global reset can be synchronous or asynchronous depending on the **HDL Code Generation > Global Settings > Reset type** parameter in the model Configuration Parameters.

For more reset considerations, see "Tips" on page 1-20.

#### Tips

#### **Reset Behavior**

- By default, the CIC Decimator block connects the generated HDL global reset to only the control path registers. The two reset parameters, **Enable reset input port** and **Use HDL global reset**, connect a reset signal to the data path registers. Because of the additional routing and loading on the reset signal, resetting data path registers can reduce synthesis performance.

- The **Enable reset input port** parameter enables the **reset** port on the block. The reset signal implements a local synchronous reset of the data path registers. For optimal use of FPGA resources, this option does not connect the reset signal to registers targeted to the DSP blocks of the FPGA.

- The **Use HDL global reset** parameter connects the generated HDL global reset signal to the data path registers. This parameter does not change the appearance of the block or modify simulation behavior in Simulink. The generated HDL global reset can be synchronous or asynchronous depending on the **HDL Code Generation** > **Global Settings** > **Reset type** parameter in the model Configuration Parameters. Depending on your device, using the global reset might move registers out of the DSP blocks and increase resource use.

- When you select the **Enable reset input port** and **Use HDL global reset** parameters together, the global and local reset signals clear the control and data path registers.

#### **Reset Considerations for Generated Test Benches**

- FPGA-in-the-loop (FIL) initialization provides a global reset but does not automatically provide a local reset. With the default reset parameters, the data path registers that are not reset can result in FIL mismatches if you run the FIL model more than once without resetting the board. Select Use HDL global reset to reset the data path registers automatically, or select Enable reset input port and assert the local reset in your model so the reset signal becomes part of the Simulink FIL test bench.

- The generated HDL test bench provides a global reset but does not automatically provide a local reset. With the default reset parameters and the default register reset Configuration Parameters, the generated HDL code includes an initial simulation value for the data path registers. However, if you are concerned about X-propagation in your design, you can set the HDL Code Generation > Global Settings > Coding style > No-reset register initialization parameter in Configuration Parameters to Do not initialize. In this case, with the default block reset parameters, the data path registers that are not reset can cause X-propagation on the data path at the start of HDL simulation. Select Use HDL global reset to reset the data path registers automatically, or select Enable reset input port and assert the local reset in your model so the reset signal becomes part of the generated HDL test bench.

#### Algorithms

#### **CIC Decimation Filter**

The transfer function of a CIC decimation filter is

$$H(z) = \left[\sum_{k=0}^{RM-1} z^{-k}\right]^{N} = \frac{\left(1-z^{-RM}\right)^{N}}{\left(1-z^{-1}\right)^{N}} = \frac{1}{\left(1-z^{-1}\right)^{N}} \cdot \frac{\left(1-z^{-RM}\right)^{N}}{1} = H_{\mathrm{I}}N(z) \cdot H_{\mathrm{c}}N(z) \,.$$

•  $H_{\rm I}$  is the transfer function of the integrator part of the CIC filter.

- $H_{\rm C}$  is the transfer function of the comb part of the CIC filter.

- *N* is the number of sections. The number of sections in a CIC filter is defined as the number of sections in either the comb part or integrator part of the filter. This value does not represent the total number of sections throughout the entire filter.

- *R* is the decimation factor.

- *M* is the differential delay.

#### **CIC Filter Structure**

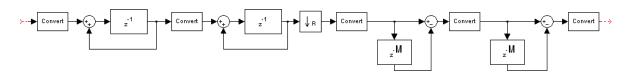

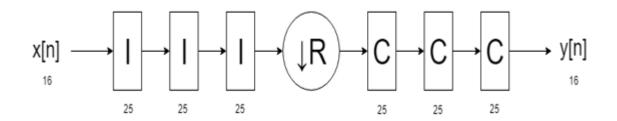

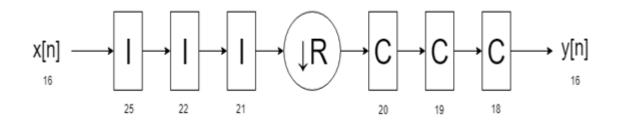

The CIC Decimator block has the CIC filter structure shown in this figure. The structure consists of N sections of cascaded integrators, a rate change factor of R, and N sections of cascaded comb filters [1].

You can locate the unit delay in the integrator part of the CIC filter in either the feedforward or feedback path. These two configurations yield an identical filter frequency response. However, the numerical outputs from these two configurations are different due to the latency of the block. Because this configuration is preferred for HDL implementation, this block puts the unit delay in the feedforward path of the integrator.

#### **Fixed and Variable Decimation**

The block downsamples the integrator stage output using R, either based on the fixed decimation rate provided using the **Decimation factor (R)** parameter or the variable decimation rate provided using the **R** input port. At the downsampler stage, the block uses a counter to count the valid input samples, which depend on the decimation rate. Whenever the decimation rate changes, the block resets and starts a new calculation from the next sample. This mechanism prevents the block from accumulating false values. Then, the block provides the decimated output to the comb part of the CIC filter.

#### **Gain Correction**

The gain of the block is given by  $Gain = (R \times M)^N$ .

- *R* is the **Decimation factor (R)** parameter value.

- *M* is the **Differential delay (M)** parameter value.

- *N* is the **Number of sections (N)** parameter value.

The block implements gain correction in two parts: coarse gain and fine gain. In coarse gain correction, the block calculates the shift value, adds the shift value to the fractional bits to create a numeric type, and performs a bit-shift left and reinterpretcast. In fine gain correction, the block divides the remaining gain with the coarse gain if the gain is not a power of 2. Then, the block multiplies the corrected coarse gain corrected value with the inverse value of the fine gain. Before the block starts processing, all possible shift and fine gain values are precalculated and stored in an array.

You can modify this equation as  $Gain = 2^{cGain} \ge fGain$ . In this equation, *cGain* is the coarse gain, and *fGain* is the fine gain. These gains are given by these equations.

- $cGain = floor(log_2Gain)$

- $fGain = Gain/2^{cGain} = Gain \ge 2^{-cGain}$

To perform gain correction when the **Decimation factor source** parameter is set to Input port, the block sets the output data type configured with the maximum decimation rate and bit-shifts left for all of the values under the maximum decimation rate. The bit-shift value is equal to  $Maximum \ gain \ - \log_2(current \ gain)$ .

#### **Output Data Type**

The block outputs data based on the output data type selection. Consider a block with *R*, *M*, and *N* values of 8, 1, and 3, respectively, and an input width of 16. The output word length is calculated as  $B_{\text{Out}} = B_{\text{In}} + [\log_2(Gain)]$ .

- $Gain = (R \ge M)^N$

- $B_{\text{In}}$  is the input word length.

- $B_{\text{Out}}$  is the output word length.

When you set the **Output data type** parameter to Full precision, the block outputs data with a word length of 25 by adding 9 gain bits to the input word length of 16.

When you set the **Output data type** parameter to Same word length as input, the block outputs data with a word length of 16, which is the same length as the input word length. The internal integrator and comb stages use the full-precision data type with 25 bits.

When you set the **Output data type** parameter to Minimum section word lengths and the **Output word length** parameter to 16, the block outputs data with a word length of 16. In this case, the block changes the bit width at each stage, based on the pruning algorithm.

If the **Output word length** parameter value is less than the number of bits required at the block output, the least significant bits (LSBs) at the earlier stages are pruned. The Hogenauer algorithm [1]

provides the number of LSBs to discard at each stage. This algorithm minimizes the loss of information in the output data.

#### Latency

The latency of the block changes depending on the type of input, the decimation you specify, the number of sections, and the value of the **Gain correction** parameter. This table shows the latency of the block. *N* is the number of sections and *vecLen* is the length of the vector.

| Input<br>Data | Output<br>Data | Decimation<br>Type | Gain<br>Correction | Latency in Clock Cycles                                                    |

|---------------|----------------|--------------------|--------------------|----------------------------------------------------------------------------|

| Scalar        | Scalar         | Fixed              | off                | 3 + N. When $R = 1, 2 + N$ .                                               |

|               |                |                    | on                 | 3 + N + 9. When $R = 1$ , $2 + N + 9$ .                                    |

| Scalar        | Scalar         | Variable           | off                | $4 + N$ . When $R_{max} = 1, 3 + N$ .                                      |

|               |                |                    | on                 | $4 + N + 9$ . When $R_{max} = 1$ , $3 + N + 9$ .                           |

| Vector        | Scalar         | Fixed              | off                | $ floor((vecLen - 1) \ge (N/vecLen)) + 1 + N + (2 + (vecLen + 1) \ge N ) $ |

|               |                |                    | on                 | floor((vecLen - 1) x (N/vecLen)) + 1 + N + (2 + (vecLen + 1) x N) + 9      |

| Vector        | Vector         | Fixed              | off                | $ floor((vecLen - 1) \ge (N/vecLen)) + 1 + N + (2 + (vecLen + 1) \ge N ) $ |

|               |                |                    | on                 | floor((vecLen - 1) x (N/vecLen)) + 1 + N + (2 + (vecLen + 1) x N) + 9      |

**Note** For vector inputs, the block does not support variable decimation.

#### Scalar Input

This section shows the output of the block for a scalar input with different *R*, *M*, and *N* values.

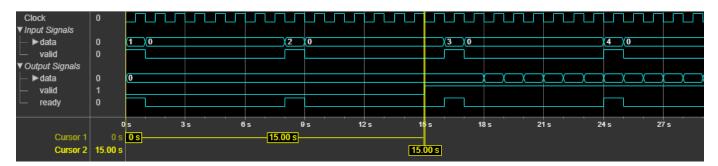

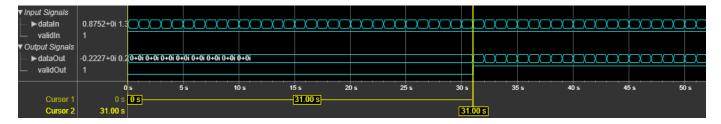

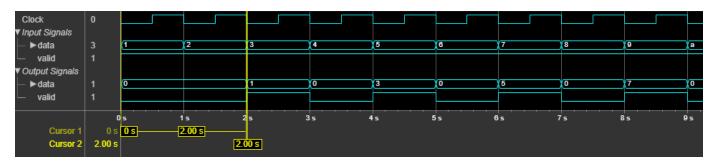

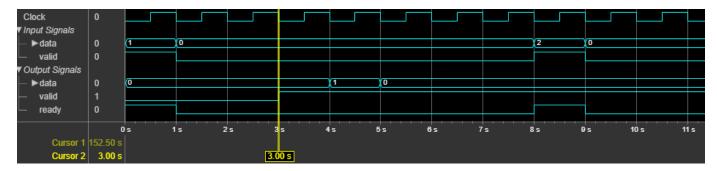

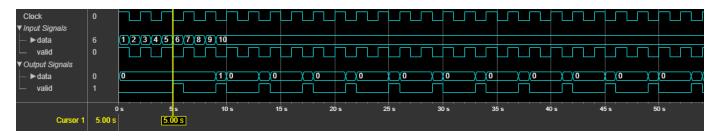

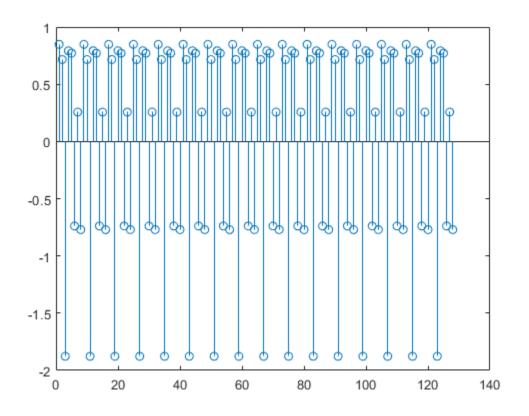

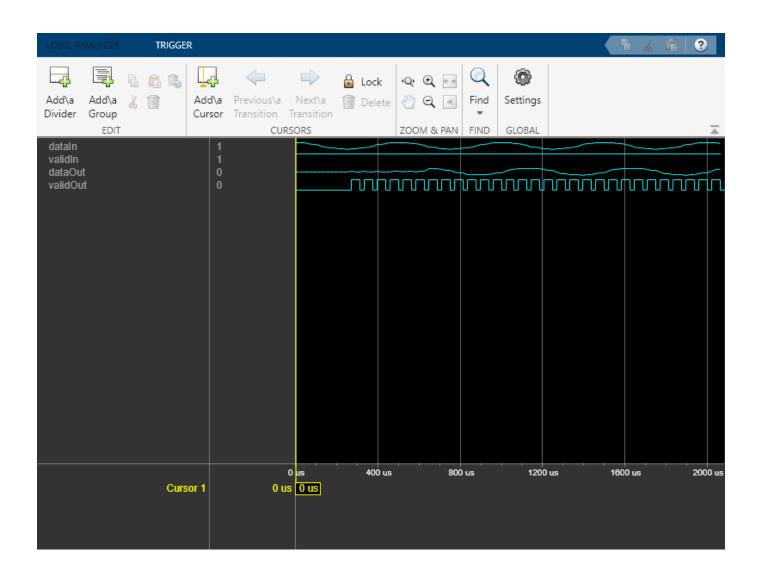

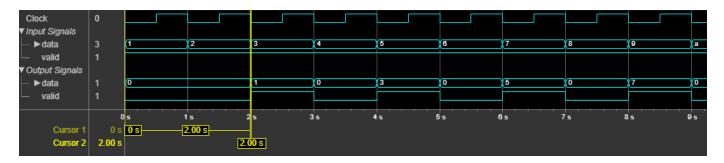

This figure shows the output of the block with the default configuration (that is, with a fixed decimation rate and R, M, and N values of 2, 1, and 2, respectively). The block returns valid output data at every second cycle based on the fixed **Decimation factor (R)** parameter value of 2. The latency of the block is 5 clock cycles and is calculated as 3 + N, where N is the number of sections.

| Clock<br>▼ Input Signals | 0      |       |         |      |       |    |      |                |                                                 |       |       |         |              |

|--------------------------|--------|-------|---------|------|-------|----|------|----------------|-------------------------------------------------|-------|-------|---------|--------------|

| — ▶data                  | 6      | 12345 | 6 7 8 9 | 10   |       |    |      |                |                                                 |       |       |         |              |

| ulid valid               | 0      |       |         |      |       |    |      |                |                                                 |       |       |         |              |

| ▼ Output Signals         |        |       |         |      |       |    |      |                |                                                 |       |       |         |              |

| — Þdata                  | 0      | 0     |         | 1 0  | )(0 ) |    | )(0  | <u>( )(0 )</u> | <u>() () () () () () () () () () () () () (</u> | ()(0  |       | ()(0))( | <u>xo</u> xx |

| - valid                  |        |       |         |      |       |    |      |                |                                                 |       |       |         |              |

|                          | (      | 0 s   | 5 s     | 10 s | 15 s  | 20 | )s 2 | 15 s 3         | 0s 3                                            | 5s 41 | 0s 48 | ōs 5    | 50 s         |

| Cursor 1                 | 5.00 s | 5     | .00 s   |      |       |    |      |                |                                                 |       |       |         |              |

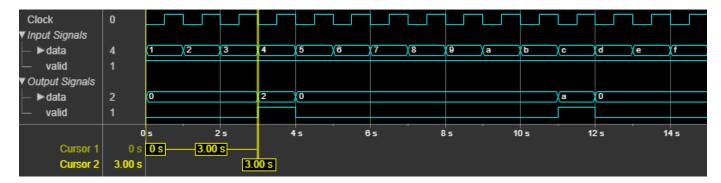

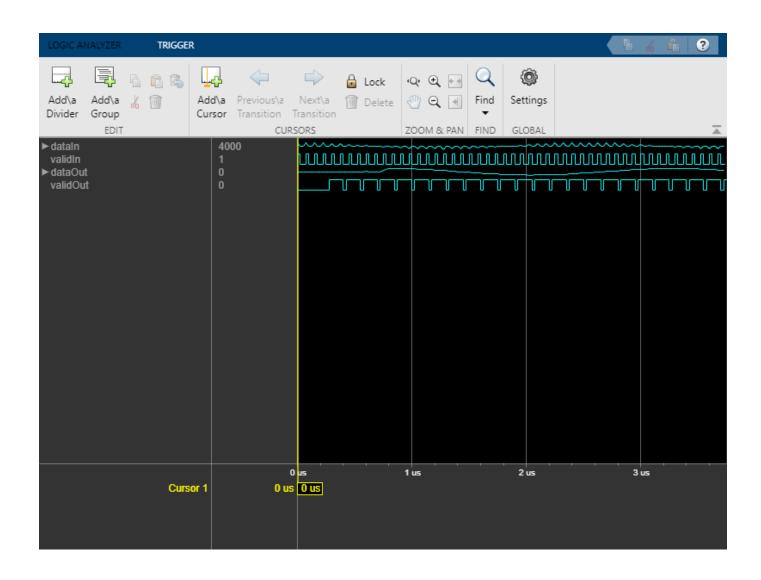

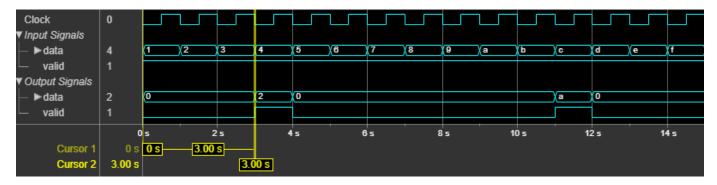

This figure shows the output of the block with a fixed decimation rate, R, M, and N values of 8, 1, and 3, respectively, and the **Gain correction** parameter selected. The block returns valid output data at every eighth cycle based on the fixed **Decimation factor (R)** parameter value of 8. The latency of the block is 15 clock cycles and is calculated as 3 + N + 9, where N is the number of sections.

| Clock            | 0       |       |            |      |      |        |      |       |        |       |       |       |        |

|------------------|---------|-------|------------|------|------|--------|------|-------|--------|-------|-------|-------|--------|

| ▼ Input Signals  |         |       |            |      |      |        |      |       |        |       |       |       |        |

| — Þdata          | 10      | 12345 | 6 7 8 9 10 |      |      |        |      |       |        |       |       |       |        |

| - valid          | 0       |       |            |      |      |        |      |       |        |       |       |       |        |

| ▼ Output Signals |         |       |            |      |      |        |      |       |        |       |       |       |        |

| — Þdata          | 0       | 0     |            |      |      |        |      | ()(0  |        |       | ) )(0 |       |        |

| - valid          |         |       |            |      |      |        |      |       |        |       |       |       |        |

|                  |         |       |            |      |      |        |      |       |        |       |       |       |        |

|                  |         | Ds 5  | s 1        | 0s 1 | is 2 | 10s 2! | 5s 3 | 0 s 3 | 15s 41 | 0s 48 | 5s 5  | 0s 55 | s 60 s |

| Cursor 1         | 15.00 s |       |            | 15   | 00 s |        |      |       |        |       |       |       |        |

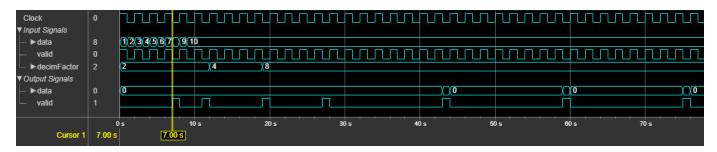

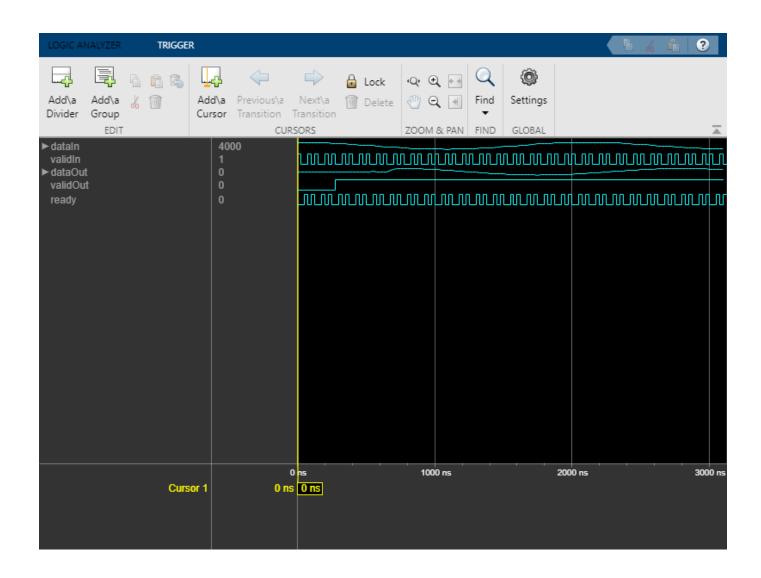

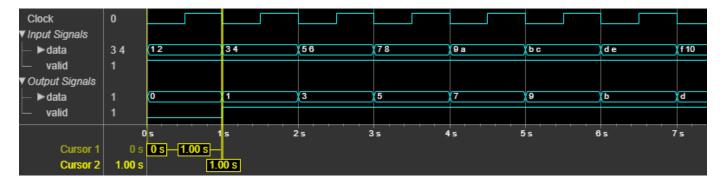

This figure shows the output of the block with variable decimation rate (**R** input port) values of 2, 4, and 8 and with *M* and *N* values of 1 and 3, respectively. In this case, the **Gain correction** parameter is cleared. The block returns valid output data at the second, fourth, and eighth cycles corresponding to the **R** port values 2, 4, and 8, respectively. The block accepts **R** port value changes only when the **valid** input port is 1. The latency of the block is 7 clock cycles and is calculated as 4 + N, where *N* is the number of sections.

| Clock            | 0      | hnn     |          |    | uп |    | าาา  |   | ПΠ  | ллл | nnn |      | nnn |     | П |

|------------------|--------|---------|----------|----|----|----|------|---|-----|-----|-----|------|-----|-----|---|

| ▼Input Signals   |        |         |          |    |    |    |      |   |     |     |     |      |     |     |   |

| — ►data          | 8      | 1234567 | 9(1      | 0  |    |    |      |   |     |     |     |      |     |     |   |

| — valid          | 0      |         | ட        |    |    |    | ᠋᠘᠘  |   | ПΠ  |     |     | ւր   |     |     | Π |

| decimFactor      | 2      | 2       |          | 4  | 8) |    |      |   |     |     |     |      |     |     |   |

| ▼ Output Signals |        |         |          |    |    |    |      |   |     |     |     |      |     |     |   |

| — Þdata          | 0      | 0       |          |    |    |    |      |   | X   | 0   |     | ) (0 |     | X   | 0 |

| - valid          |        |         |          |    |    |    |      |   |     |     |     |      |     |     |   |

|                  |        |         | L        |    |    |    |      |   |     |     |     |      |     |     |   |

|                  | ( C    | )s      | <u> </u> | )s | 20 | )s | 30 s | 4 | 0 s | 5   | 0 s | 60 s | 70  | ) s |   |

| Cursor 1         | 7.00 s | 7.      | )0 s     |    |    |    |      |   |     |     |     |      |     |     |   |

#### **Vector Input**

This section shows the output of the block for a vector input with different *R*, *M*, and *N* values.

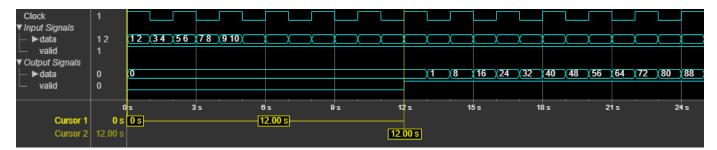

This figure shows the output of the block for a two-element column vector input with the default configuration, (that is, with a fixed decimation rate and R, M, and N values of 2, 1, and 2, respectively). The latency of the block is 12 clock cycles.

| Clock<br>▼Input Signals       | 1       |      |      |     |                |          |      |   |     |   |     |      |            |           |      |    |     |     | 1                 |                   |      |                   | 7                |            |

|-------------------------------|---------|------|------|-----|----------------|----------|------|---|-----|---|-----|------|------------|-----------|------|----|-----|-----|-------------------|-------------------|------|-------------------|------------------|------------|

| – ▶data                       | 12      | 12 3 | 4 56 | 78  | <u>x9 10 x</u> | X        | χ    | χ | X   | χ | χ   | X    | χ          | χ         | X    | χ  | χ   | X   | χ                 | χ                 | X    | χ                 | χ                |            |

| └── valid<br>▼ Output Signals | 1       |      |      |     |                |          |      |   |     |   |     |      |            |           |      |    | ,   |     |                   |                   |      |                   |                  |            |

| — ►data<br>— valid            | 0<br>0  | 0    |      |     |                |          |      |   |     |   |     |      | <u>)</u> 1 | <u>(8</u> | 16   | 24 | (32 | 40  | <mark>(</mark> 48 | <mark>(</mark> 56 | 64   | <mark>(</mark> 72 | <mark>(80</mark> | <u> 88</u> |

|                               | (       | ) s  |      | 3 s |                | 6 s      |      |   | 9 s |   | 1   | 2 5  |            |           | 15 s |    | 1   | 8 s |                   |                   | 21 s |                   | 2                | 4is        |

| Cursor 1                      | 0 s     | 0 s  |      |     |                | <u> </u> | 00 s |   |     |   |     |      |            |           |      |    |     |     |                   |                   |      |                   |                  |            |

| Cursor 2                      | 12.00 s |      |      |     |                |          |      |   |     |   | 12. | 00 s |            |           |      |    |     |     |                   |                   |      |                   |                  |            |

This figure shows the output of the block for an eight-element column vector input with a fixed decimation rate, R, M, and N values of 8, 1, and 3, respectively, and the **Gain correction** parameter selected. The latency of the block is 44 clock cycles.

| Clock           | 0                               | MMMM                                    | hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh | hhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhhh | www   | տուր  | nnn | www.www |

|-----------------|---------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-------|-------|-----|---------|

| ▼ Input Signals |                                 |                                         |                                         |                                         |       |       |     |         |

| — ►data         | 353 354 355 356 357 358 359 360 | 000000000000000000000000000000000000000 |                                         |                                         |       |       |     |         |

| — valid         |                                 |                                         |                                         |                                         |       |       |     |         |

| ▼Output Signals |                                 |                                         |                                         |                                         |       |       |     |         |

| — 🕨 data        | 0                               | 0                                       |                                         |                                         |       | Х     |     |         |

| — valid         |                                 |                                         |                                         |                                         |       |       |     |         |

|                 |                                 |                                         | 10 s 2                                  | 0 s 3                                   | 0 s 4 | l0 s  | 50  | s 60 s  |

| Cursor 1        |                                 | s<br>0 s                                | 105 2                                   |                                         | -     | 03    | 50  | 5 005   |

| Cursor 2        |                                 |                                         |                                         |                                         |       | 44.00 | 3   |         |

| Cuisoi z        | 44.00 S                         |                                         |                                         |                                         |       | 44.00 | 2   |         |

#### Performance

The performance of the synthesized HDL code varies with your target and synthesis options. It also varies based on the input data type.

This table shows the resource and performance data synthesis results of the block for a scalar input of type fixdt(1, 16, 0) with fixed and variable decimation rates and for a two-element column vector input with a fixed decimation rate when *R*, *M*, and *N* are 2, 1, and 2, respectively. The generated HDL is targeted to the Xilinx Zynq- 7000 ZC706 Evaluation Board.

| Input Data | Decimation Type | Slice LUTs | -   | Maximum Frequency in<br>MHz |

|------------|-----------------|------------|-----|-----------------------------|

| Scalar     | Fixed rate      | 101        | 166 | 711.74                      |

|            | Variable rate   | 206        | 186 | 441.70                      |

| Vector     | Fixed rate      | 218        | 627 | 624.61                      |

The resources and frequencies vary based on the type of input data and the values of R, M, and N, as well as other parameter values selected in the block mask. Using a vector input can increase the throughput, however, doing so also increases the number of hardware resources that the block uses.

### **Version History**

Introduced in R2019b

#### Moved to DSP HDL Toolbox from DSP System Toolbox

Behavior changed in R2022a

Before R2022a, this block was named CIC Decimation HDL Optimized and was included in the DSP System Toolbox<sup>™</sup> DSP System Toolbox HDL Support library.

#### Changes to decimation factor parameters

Behavior changed in R2022a

You can now set the decimation factor to 1. In previous releases, a decimation factor of 1 was invalid.

| Configuration              | Before R2022a                                                                                                                                             | After 2022a                                                                                                                                                                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Variable decimation factor | Select the <b>Variable decimation</b><br>parameter and set the<br><b>Decimation factor (R)</b><br>parameter to the maximum<br>expected decimation factor. | Set the <b>Decimation factor</b><br><b>source</b> parameter to Input<br>port and set the <b>Decimation</b><br><b>factor (Rmax)</b> parameter to<br>the maximum expected<br>decimation factor. The<br><b>decimFactor</b> port is renamed<br>to <b>R</b> . |

| Fixed decimation factor    | Clear the <b>Variable decimation</b><br>parameter and set the<br><b>Decimation factor (R)</b><br>parameter to the desired<br>decimation factor.           | Set the <b>Decimation factor</b><br><b>source</b> parameter to Property<br>and set the <b>Decimation factor</b><br><b>(R)</b> to the desired decimation<br>factor.                                                                                       |

#### **High-throughput interface**

The block accepts and returns a column vector of elements that represent samples in time. The input vector can contain up to 64 samples. When you use frame-based input, you must use a fixed decimation factor.

#### Gain correction and programmable decimation factor

You can optionally enable automatic gain correction. You can also specify the decimation factor as an input port.

#### References

[1] Hogenauer, E. "An Economical Class of Digital Filters for Decimation and Interpolation." IEEE Transactions on Acoustics, Speech, and Signal Processing 29, no. 2 (April 1981): 155–62. https://doi.org/10.1109/TASSP.1981.1163535.

#### **Extended Capabilities**

#### C/C++ Code Generation

Generate C and C++ code using Simulink<sup>®</sup> Coder<sup>m</sup>.

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

#### HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

$\ensuremath{\mathsf{HDL}}$  Coder provides additional configuration options that affect  $\ensuremath{\mathsf{HDL}}$  implementation and synthesized logic.

#### **HDL Architecture**

This block has one default HDL architecture.

#### HDL Block Properties

| ConstrainedOutputPi<br>peline | Number of registers to place at the outputs by moving existing delays within your design. Distributed pipelining does not redistribute these registers. The default is $0$ . For more details, see "ConstrainedOutputPipeline" (HDL Coder). |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| InputPipeline                 | Number of input pipeline stages to insert in the generated code. Distributed pipelining and constrained output pipelining can move these registers. The default is $0$ . For more details, see "InputPipeline" (HDL Coder).                 |

| OutputPipeline                | Number of output pipeline stages to insert in the generated code.<br>Distributed pipelining and constrained output pipelining can move these<br>registers. The default is 0. For more details, see "OutputPipeline" (HDL<br>Coder).         |

#### See Also

#### Objects

dsphdl.CICDecimator|dsphdl.CICInterpolator

Blocks

CIC Interpolator

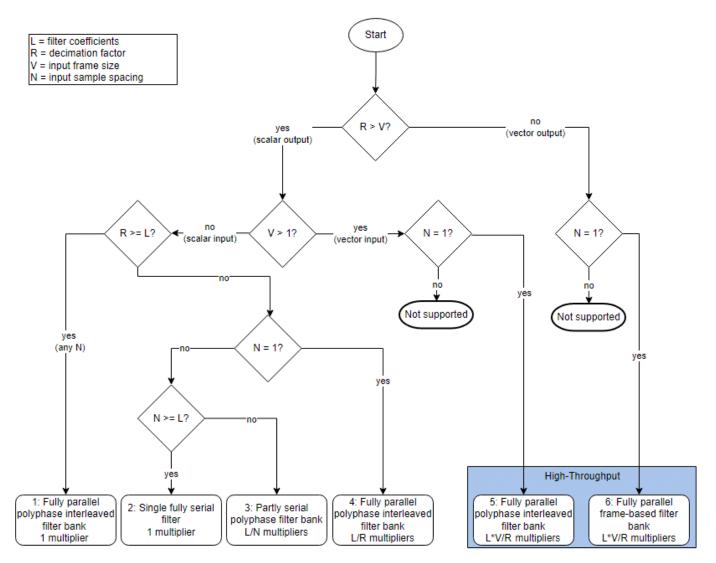

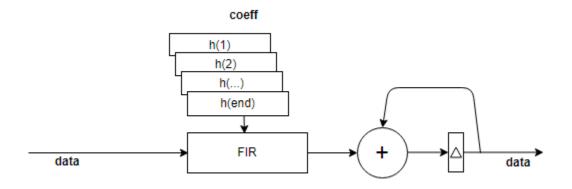

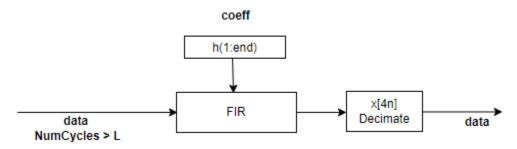

## **Discrete FIR Filter**

Finite impulse response filter

Library: DSP HDL Toolbox / Filtering

#### Description

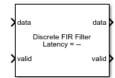

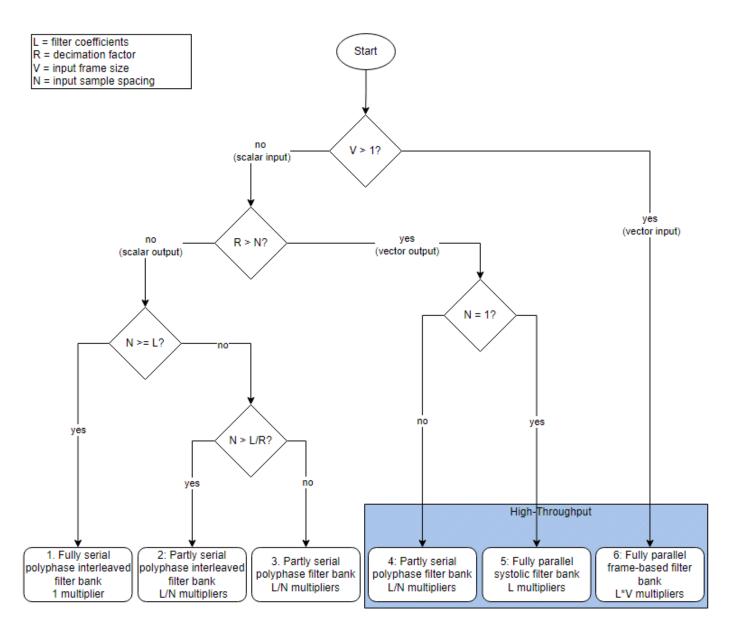

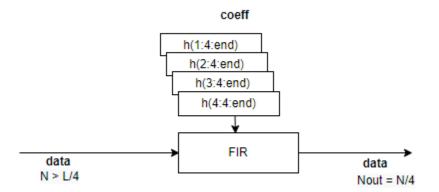

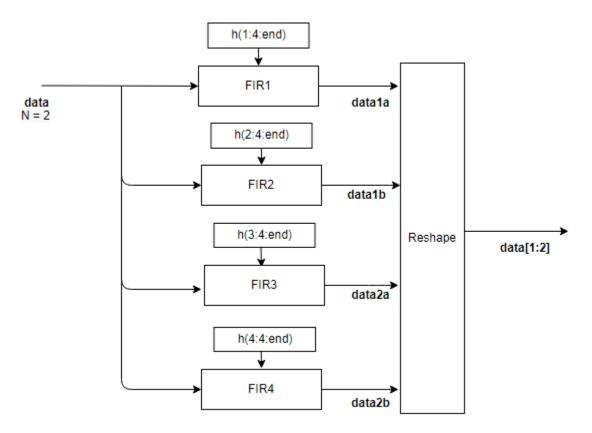

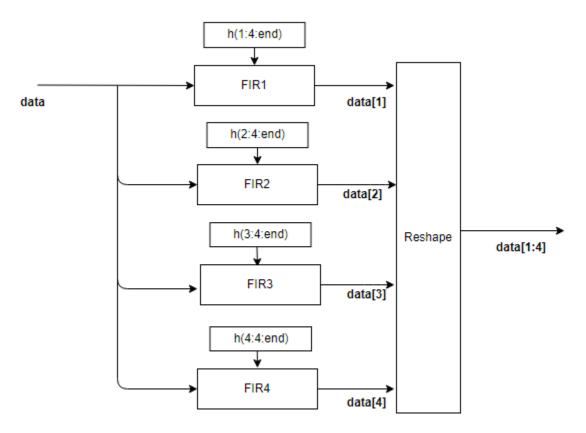

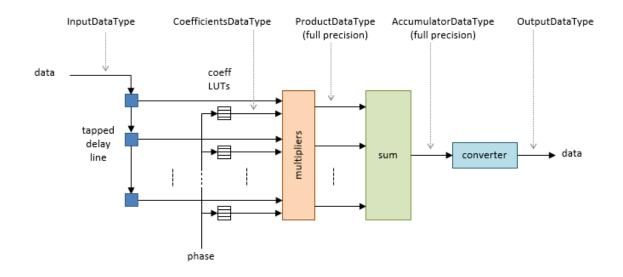

The Discrete FIR Filter block models finite-impulse response filter architectures optimized for HDL code generation. The block accepts scalar or frame-based input, and provides an option for programmable coefficients. It provides a hardware-friendly interface with input and output control signals. To provide a cycle-accurate simulation of the generated HDL code, the block models architectural latency including pipeline registers and resource sharing.

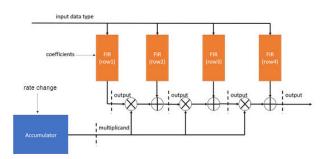

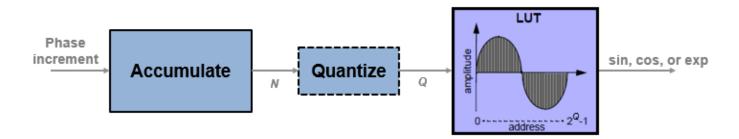

The block provides three filter structures. The direct form systolic architecture provides a fully parallel implementation that makes efficient use of Intel® and Xilinx DSP blocks. The direct form transposed architecture is a fully parallel implementation and is suitable for FPGA and ASIC applications. The partly serial systolic architecture provides a configurable serial implementation that makes efficient use of FPGA DSP blocks. For a filter implementation that matches multipliers, pipeline registers, and pre-adders to the DSP configuration of your FPGA vendor, specify your target device when you generate HDL code.

All three filter structures remove multipliers for zero-valued coefficients, such as in half-band filters and Hilbert transforms. When you use scalar input data, all filter structures share multipliers for symmetric and antisymmetric coefficients. Frame-based filters do not implement symmetry optimization.

The latency between valid input data and the corresponding valid output data depends on the filter structure, serialization options, the number of coefficients, and whether the coefficient values provide optimization opportunities. For details of structure and latency, see the "Algorithm" on page 1-34 section.

For a FIR filter with multichannel support, use the Discrete FIR Filter block instead.

#### Ports

Input

#### data — Input data

scalar or column vector of real or complex values

Input data, specified as a scalar or column vector of real or complex values. The vector size must be a power of 2 in the range from 1 to 64. When the input data type is an integer type or a fixed-point type, the block uses fixed-point arithmetic for internal calculations.

double and single data types are supported for simulation, but not for HDL code generation.

Data Types: fixed point | single | double | int8 | int16 | int32 | uint8 | uint16 | uint32

#### valid — Indicates valid input data

scalar

Control signal that indicates if the input data is valid. When **valid** is 1 (true), the block captures the values from the input **data** port. When **valid** is 0 (false), the block ignores the values from the input **data** port.

Data Types: Boolean

#### coeff - Filter coefficients

real or complex row vector

Filter coefficients, specified as a row vector of real or complex values. You can change the input coefficients at any time. When you use scalar input data, the size of the coefficient vector depends on the size and symmetry of the sample coefficients specified in the **Coefficients prototype** parameter. The prototype specifies a sample coefficient vector that is representative of the symmetry and zero-valued locations of the expected input coefficients. The block uses the prototype to optimize the filter by sharing multipliers for symmetric or antisymmetric coefficients, and removing multipliers for zero-valued coefficients. Therefore, provide only the nonduplicate coefficients at the port. For example, if you set the **Coefficients prototype** parameter to a symmetric 14-tap filter, the block expects a vector of 7 values on the **coeff** input port. You must still provide zeros in the input **coeff** vector for the nonduplicate zero-valued coefficients.

When you use frame-based input data, the block does not optimize the filter for coefficient symmetry. The block still uses the **Coefficients prototype** to remove multipliers for zero-valued coefficients. At the **coeff** input port, specify a vector that is the same size as the prototype.

double and single data types are supported for simulation, but not for HDL code generation.

#### Dependencies

To enable this port, set **Coefficients source** to Input port (Parallel interface).

Data Types: single | double | int8 | int16 | int32 | uint8 | uint16 | uint32 | fixed point

#### reset — Clears internal states

scalar

Control signal that clears internal states. When **reset** is 1 (true), the block stops the current calculation and clears internal states. When the **reset** is 0 (false) and the input **valid** is 1 (true), the block captures data for processing.

For more reset considerations, see the "Reset Signal" section on the "Hardware Control Signals" page.

#### Dependencies

To enable this port, on the **Control Ports** tab, select **Enable reset input port**.

Data Types: Boolean

#### Output

#### data — Filtered output data

scalar or column vector of real or complex values